主要功能

-

支持测试 400 MHz、533 MHz、667 MHz、800 MHz、1066 MHz 和自定义速度的 DDR2 信号

-

通过测量大量周期并报告统计结果来获得对 DDR2 接口的信心的最快方法

-

捕获并在报告中显示带完整注释的最坏情况测量屏幕截图,包括信号标识和相关电压电平

-

Stop on test/failure功能允许用户暂停并在示波器显示屏上查看相应测试项的测量值

-

完整覆盖JESD79-2E 和 JESD208 JEDEC 规范以及 Intel DDR2 667/800 JEDEC 规范附录 Rev. 1.1 和 Intel DDR2 400/ 533 JEDEC 规范附录 Rev. 1.0 所述的测试项

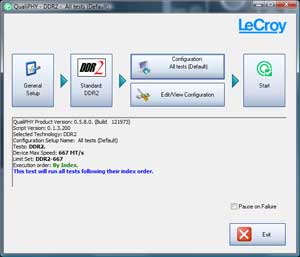

Teledyne LeCroy QPHY-DDR2 测试解决方案是评估 DDR2 内存接口的最佳方式。 QPHY-DDR400能够对533MHz、667 MHz、800 MHz、1066 MHz、2 MHz、XNUMX MHz 和自定义速度进行测量,具有符合JEDEC 规范和英特尔 JEDEC 规范附录规定的全套时钟、电气和时序测试。

Teledyne LeCroy QualiPHY 平台提供易于配置的用户界面,允许自定义测试和结果范围,向用户显示连接图以确保正确连接,并生成包含所有结果的报告,报告包括每个测试项中最坏情况测试失败的屏幕截图。 此外,QPHY-DDR2 测试的所有波形都可以保存,以便轻松分享信息或在以后重新运行测试。

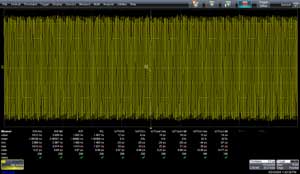

QPHY-DDR2 使用户能够提高对 DDR2 接口信号的信心。 由于 DDR2 信号易变,需要测量大量的周期。 通过在很短的时间内捕获大量周期进行测试,用户可以更加确信他们能捕捉到可信的最大和最小测量值。

除了对 DDR2 信号的自动特性测试,示波器的 QPHY-DDR2 还为 DDR2 信号提供强大的调试功能。 使用示波器中的所有高级串行数据工具,如SDA II、Eye Doctor™ II、WaveScan™ 等等,可以快速轻松地找到测试失败的根本原因。

时钟测试——执行相应 JEDEC 规范所描述的所有时钟这些测试项。 包括平均时钟周期、绝对时钟周期、平均高/低脉冲宽度、绝对高/低脉冲宽度、半周期抖动、时钟周期抖动、Cycle-to-cycle抖动和 n 周期测试的累积误差。

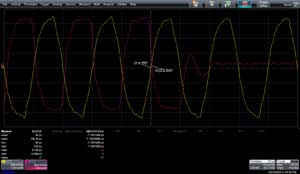

电气测试——测量 DDR2 信号的电气特性。 如上所示,SoutR 测试项测量Data、Strobe和时钟信号的斜率。 进行 1000 余次斜率测量,并在屏幕上显示最差的情况。 信号名称会注释在屏幕截图的信号上,方便理解。 此外,会通过光标向用户显示测量斜率的电压电平。

时序测试——验证特定 DDR2 事件之间的时序关系。 如上所示,tDQSCK 测试验证的Strobe输出访问时间相对时钟信号是否在相应 JEDEC 规范规定的限制范围内。 在此测试中,对所有DDR5000读信号进行了 2 次 tDQSCK 测量,并将最差情况显示在屏幕上。

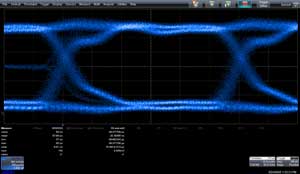

眼图——眼图是调试串行数据信号的强大工具。 QPHY-DDR2 使用户能够生成读和写Burst的眼图,以确保信号完整性,使接收器正确采样数据。

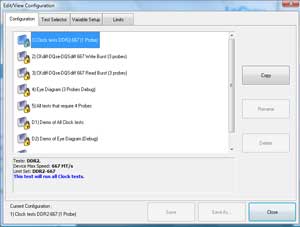

QualiPHY 具有许多预设的一致性配置,但也能让用户创建自己的配置和测试结果范围。

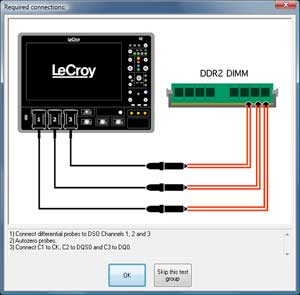

连接图提示用户进行必要的连接。

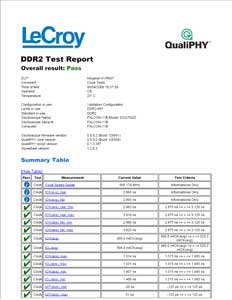

一致性报告包含所有测试值、特定测试结果范围和屏幕截图。 合规报告可以创建为 HTML、PDF 或 XML。

QualiPHY

QualiPHY 旨在减少在执行高速串行总线一致性测试上所需要的时间、精力,并提供专业知识辅导。

-

指导用户完成每个测试设置

-

按照相关的测试程序执行每次测量

-

将每个测量值与相应的规格要求进行比较

-

完整记录所有结果

-

QualiPHY 帮助用户以正确的方式进行每一次测试!

规格

时钟测试

tCK(avg) – 平均时钟周期

tCH(avg) – 平均正脉冲宽度

tCL(avg) – 平均负脉冲宽度

tCK (abs) – 绝对时钟周期

tCH(abs) – 绝对正脉冲宽度

tCL(abs) – 绝对负脉冲宽度

tJIT(duty) – 半周期抖动

tJIT(per) – 时钟周期抖动

tJIT(cc) – Cycle to Cycle周期抖动

tERR(n per) – 累积误差

高级调试

读取周期数据和选通的眼图

写入周期数据和选通的眼图

电气测试

SlewR – 输入上升沿斜率

SlewF – 输入下降沿斜率

VIH(ac) – 交流输入逻辑高电平

VIH(dc) – 直流输入逻辑高电平

VIL(ac) – 交流输入逻辑低电平

VIL(dc) – 直流输入逻辑低电平

VSWING – 输入信号最大值

峰峰值

SoutR – 输出上升沿斜率

SoutF – 输出下降沿斜率

tSLMR – 输出斜率匹配比

交流过冲峰值幅度

高于 VDDQ 的交流过冲Area

交流下冲峰值幅度

VSSQ 以下的交流下冲Area

VID(ac) – 交流差分输入电压

VIX(ac) – 交流差分输入交叉点电压

VOX(ac) – 交流差分输出交叉点电压

时序测试

tHZ(DQ) – 从 CK/CK# 开始的 DQ 高阻抗时间

tLZ(DQ) – 从 CK/CK# 开始的 DQ 低阻抗时间

tLZ(DQS) – 从 CK/CK# 开始的 DQS 低阻抗时间

tHP – CK 半脉冲宽度

tQHS – DQ Hold Skew Factor

tQH – DQS 的 DQ/DQS 输出保持时间

tDQSH – DQS 输入正脉冲宽度

tDQSL – DQS 输入负脉冲宽度

tDSS – DQS 下降沿到 CK 建立时间

tDSH – DQS Falling Edge Hold Time from CK

tWPRE——写前导

tWPST – 写后导

tRPRE——读前导

tRPST - 读后导

tDQSQ – DQS 和 DQ 之间的时延

tDQSS – DQS Latching Transition to Clock Edge

tDQSCK – 从 CK/CK# 开始的 DQS 输出访问时间

tAC – 从 CK/CK# 开始的 DQ 输出访问时间

tDS(base) – DQ 和 DM 输入建立时间

tDH(base) – DQ 和 DM 输入保持时间

tIS(base) – 地址和控制输入建立时间

tIH(base)——地址和控制输入保持时间

tDS1(base)——DQ 和 DM 输入建立时间(单端选通)

tDH1(base) – DQ 和 DM 输入保持时间(单端选通)